导航

微信

顶部

发布时间:2026-01-04 阅读: 来源:管理员

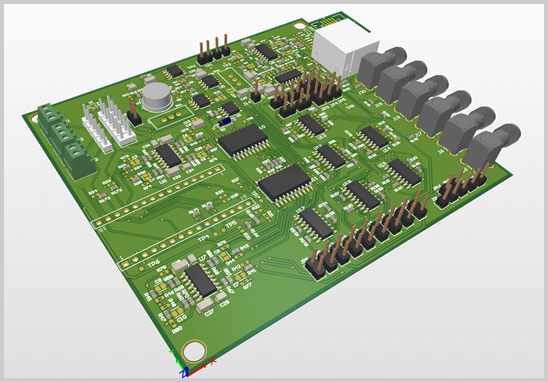

在实际项目中,很多客户在多层PCB上遇到的问题,并不是原理图画错,而是设计阶段对多层板的复杂性预估不足。等到样品回来,才发现信号不稳定、接口异常、EMI不过,甚至无法量产。

多层PCB设计真正考验的,是对信号完整性、工艺可行性以及量产稳定性的综合把控。下面从实际工程经验出发,把多层PCB设计中最核心、最容易踩坑的地方逐一讲清楚。

一个常见误区是:

原理图确认后,直接开始布局布线,层数不够再往上加。

但在多层PCB设计中,层叠结构本身就决定了后续布线能否顺利、信号是否稳定。

合理的层叠需要提前考虑几个关键问题:信号层是否有完整、连续的参考平面;高速信号是否始终“贴地”走线;电源层与地层的分布是否有利于抑制噪声。

经验上来看,多层板设计时,优先保证完整地平面往往比多加一层信号层更重要。尤其是高速接口、时钟线、差分线较多的设计,如果地层被切割或不连续,后期很容易出现难以定位的异常问题。

不少多层PCB在功能上“能跑”,但稳定性差,抗干扰能力弱,根本原因常常出在信号回流路径上。

高速信号在传输过程中,并不是单独存在的,它始终需要通过参考平面完成回流。如果信号跨越了电源分割区域、换层却没有就近的接地过孔,或者地平面被大量开槽,就会导致回流路径被迫绕行。

这种情况下,即便线宽、长度都符合要求,仍然可能出现串扰加重、辐射增强、EMI测试失败等问题。

在设计阶段,务必要保证高速信号全程对应连续的参考平面,在信号换层位置合理布置接地过孔,为回流提供最短路径。

在多层PCB设计中,阻抗问题是返工率非常高的一类问题。

很多设计在初期只关注线宽,却忽略了阻抗实际上由多个因素共同决定,包括介质厚度、介电常数、铜厚以及信号层与参考层之间的距离。

如果在设计阶段没有先确认层叠结构和板材参数,后期即便厂家能够调整工艺,也很难保证阻抗完全达标。

更稳妥的做法是,在设计前就与PCB加工方确认可用板材和层叠方案,根据目标阻抗反推线宽,并在关键高速或差分信号上预留阻抗测试结构。相关计算方法可参考 IPC-2141 阻抗设计指南。

只要涉及BGA、多引脚、高I/O器件,多层PCB设计的复杂度就会明显上升。

常见问题包括:逃线方式选择不合理,导致布线空间严重不足;过孔位置不当,影响焊接可靠性;没有提前考虑是否需要盲孔、埋孔,结果做到一半发现工艺无法实现。

在实际设计中,BGA器件必须在布局阶段就同步规划逃线策略,并结合目标PCB厂的最小线宽、最小孔径能力进行设计。焊盘是否开窗、过孔是否需要塞孔或填孔,都需要在设计阶段确认清楚,否则很容易在打样或贴装阶段暴露问题。

在多层、高密度PCB中,盲孔和埋孔确实能有效缓解布线压力,但它们并不是万能方案。

一方面,盲埋孔会显著提高PCB制造成本;另一方面,不同PCB厂在层叠次数、孔径能力、良率控制方面差异较大。如果设计时没有充分考虑量产可行性,后期很可能因为工艺限制被迫改版。

比较稳妥的做法是,优先通过优化层叠结构和布线策略解决问题,在确实必要的情况下再引入盲孔或埋孔,并提前与加工厂确认实际可执行能力。

很多问题并不是设计“画错”,而是没有考虑后续制造和测试。

例如线宽线距逼近工艺极限、孔径与板厚比例不合理、测试点不足、拼板方案不清晰等,这些都会在量产阶段放大风险。

因此,多层PCB设计不应只关注“电路是否通”,还应在设计阶段同步进行DFM(可制造性)和DFA/DFT(可装配、可测试)思考,减少后期返工与调试成本。

多层PCB设计已经不再是单纯的画板服务,而是一项涵盖电气、工艺、成本和量产稳定性的系统工程。

以深圳宏力捷电子这类专业PCB设计公司为例,通常可以在客户仅提供原理图的情况下,完成从PCB布局布线、BOM建立、元器件选型,到供应商对接、样品制作以及PCBA批量生产的完整流程。

这种一体化方式的核心价值,在于把问题前移到设计阶段解决,避免客户在打样、测试和量产过程中反复修改。

多层PCB设计,真正省钱的不是少画几层,而是一次就做对。

如果你的项目涉及多层、高速、高密度或BGA封装,设计阶段的专业性,往往决定了整个项目的成败。

提前避坑,远比后期返工更重要。

获取报价